# ABSTRACTION REFINEMENT FOR LARGE SCALE MODEL CHECKING

CHAO WANG NEC Laboratories America Princeton, New Jersey

GARY D. HACHTEL University of Colorado Boulder, Colorado

FABIO SOMENZI University of Colorado Boulder, Colorado

# Contents

| Li | st of | Figures                          | vii |

|----|-------|----------------------------------|-----|

| Li | st of | Tables                           | ix  |

| Pr | eface |                                  | xi  |

| 1. | INT   | TRODUCTION                       | 1   |

|    | 1.1   | Background                       | 3   |

|    | 1.2   | Our Contributions                | 5   |

|    | 1.3   | Organization of This Book        | 9   |

| 2. | SYI   | MBOLIC MODEL CHECKING            | 11  |

|    | 2.1   | Finite State Model               | 12  |

|    | 2.2   | Temporal Logic Property          | 16  |

|    | 2.3   | Generalized Büchi Automaton      | 22  |

|    | 2.4   | BDD-based Model Checking         | 29  |

|    | 2.5   | SAT and Bounded Model Checking   | 35  |

|    | 2.6   | Abstraction Refinement Framework | 40  |

| 3. | AB    | STRACTION                        | 43  |

|    | 3.1   | Introduction                     | 44  |

|    | 3.2   | Fine-Grain Abstraction           | 46  |

|    | 3.3   | Abstract Counterexamples         | 51  |

|    | 3.4   | Further Discussion               | 55  |

| 1. | RE    | FINEMENT                         | 59  |

|    | 4.1   | Generational Refinement          | 60  |

|    | 4.2   | Refinement Variable Selection    | 67  |

|    | 13    | Keen the Refinement Set Small    | 73  |

|     | 4.4   | Apply Sequential Don't Cares          | 76  |

|-----|-------|---------------------------------------|-----|

|     | 4.5   | Implementation and Experiments        | 78  |

|     | 4.6   | Further Discussion                    | 83  |

| 5.  | CO    | MPOSITIONAL SCC ANALYSIS              | 89  |

|     | 5.1   | Language Emptiness                    | 90  |

|     | 5.2   | SCC Partition Refinement              | 93  |

|     | 5.3   | The D'n'C Algorithm                   | 96  |

|     | 5.4   | The Composition Policies              | 102 |

| 6.  | DIS   | JUNCTIVE DECOMPOSITION                | 107 |

|     | 6.1   | Adaptive Popcorn-line Policy          | 107 |

|     | 6.2   | Disjunctive Decomposition Theorem     | 110 |

|     | 6.3   | Guided Search for Fair Cycles         | 112 |

|     | 6.4   | Implementation and Experiments        | 117 |

|     | 6.5   | Further Discussion                    | 122 |

| 7.  | FAI   | R SIDE IMAGE COMPUTATION              | 127 |

|     | 7.1   | Symbolic Image Computation            | 128 |

|     | 7.2   | The Far Side Image Algorithm          | 131 |

|     | 7.3   | Experiments                           | 135 |

|     | 7.4   | Discussion of Hypothesis              | 139 |

| 8.  | RE    | FINE SAT DECISION ORDERING            | 143 |

|     | 8.1   | Unsatisfiability Proof as Abstraction | 144 |

|     | 8.2   | Refine the Decision Ordering          | 149 |

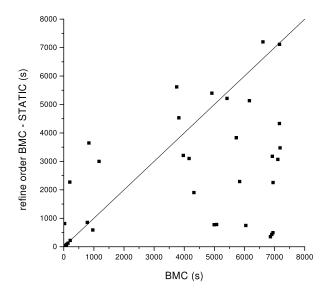

|     | 8.3   | Experimental Analysis                 | 153 |

|     | 8.4   | Further Discussion                    | 159 |

| 9.  | CO    | NCLUSIONS                             | 161 |

|     | 9.1   | Summary of Results                    | 161 |

|     | 9.2   | Future Directions                     | 163 |

| Re  | feren | ices                                  | 165 |

| Inc | dex   |                                       | 183 |

# List of Figures

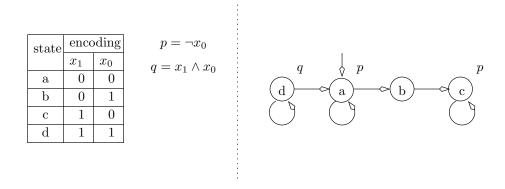

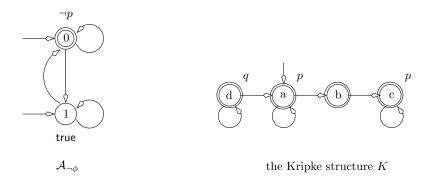

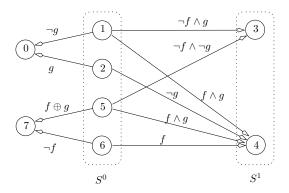

| 2.1 | An example of the Kripke structure.                                      | 13 |

|-----|--------------------------------------------------------------------------|----|

| 2.2 | A sequential circuit example.                                            | 14 |

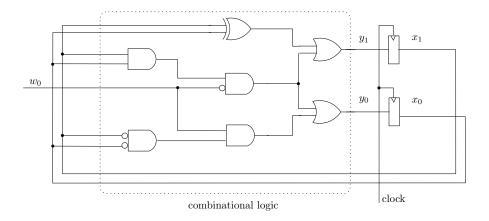

| 2.3 | A Kripke structure and its computation tree.                             | 19 |

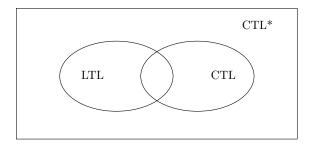

| 2.4 | The relationship among LTL, CTL, and CTL*.                               | 20 |

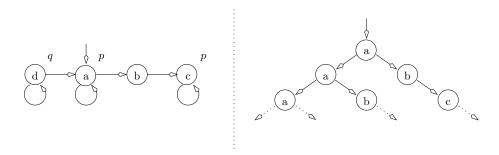

| 2.5 | An LTL model checking example.                                           | 24 |

| 2.6 | Two terminal generalized Büchi automata.                                 | 32 |

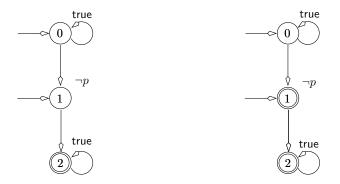

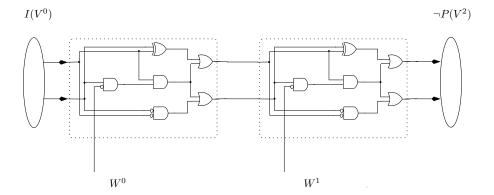

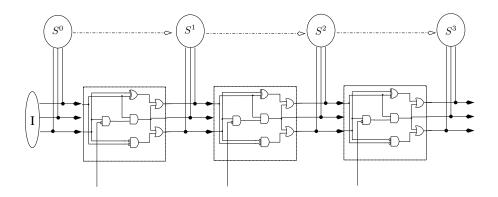

| 2.7 | A bounded model checking instance.                                       | 37 |

| 2.8 | The DLL Boolean SAT procedure.                                           | 39 |

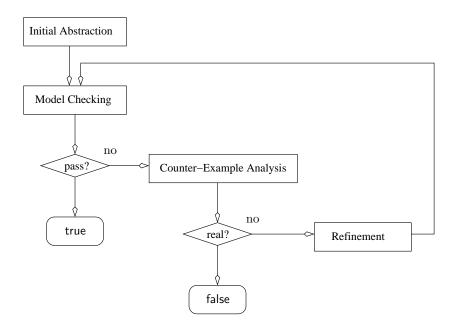

| 2.9 | The abstraction refinement framework.                                    | 41 |

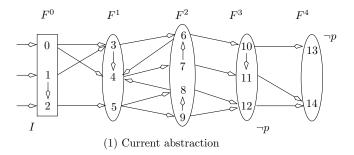

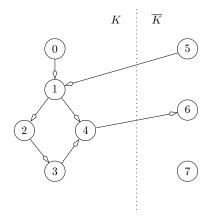

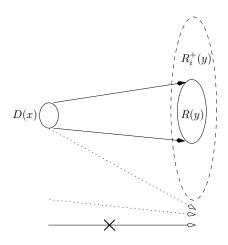

| 3.1 | Illustration of fine-grain abstraction.                                  | 48 |

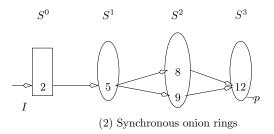

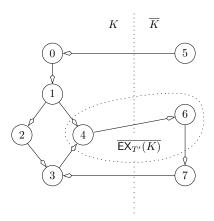

| 3.2 | Ariadne's bundle of synchronous onion rings.                             | 52 |

| 3.3 | Multi-thread concretization test.                                        | 54 |

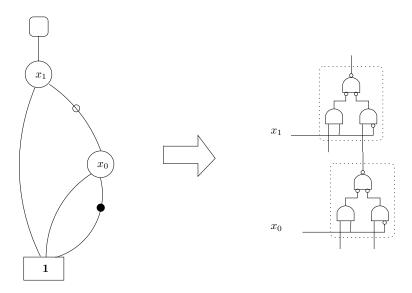

| 3.4 | Translating a BDD into a combinational circuit.                          | 55 |

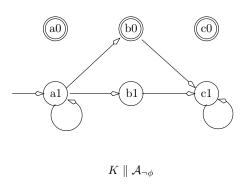

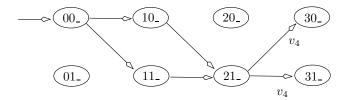

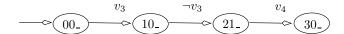

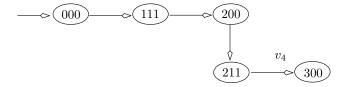

| 4.1 | An example for abstraction refinement.                                   | 60 |

| 4.2 | The generational refinement process.                                     | 62 |

| 4.3 | The effect of generational refinement, with refinement minimization.     | 63 |

| 4.4 | The GRAB abstraction refinement algorithm.                               | 65 |

| 4.5 | Illustration of the winning positions.                                   | 69 |

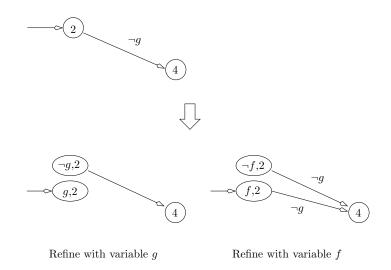

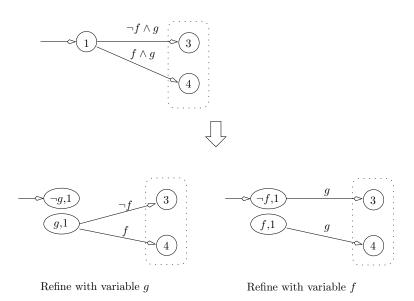

| 4.6 | An example for state splitting.                                          | 70 |

| 4.7 | Another example for state splitting.                                     | 70 |

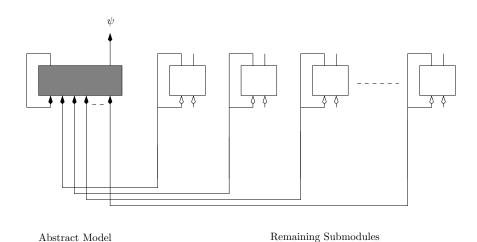

| 4.8 | Sequential Don't Cares from remaining submodules.                        | 76 |

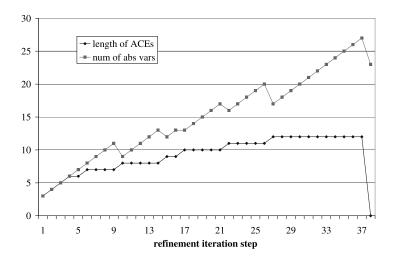

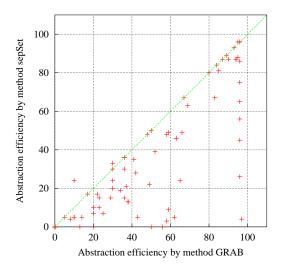

| 4.9 | Comparing the abstraction efficiency of different refinement algorithms. | 80 |

|     | remement argorithms.                                                     | 00 |

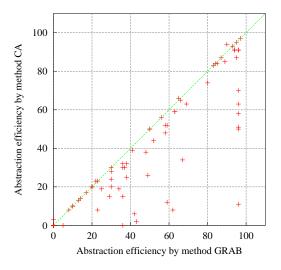

| 4.10 | The CPU time distribution among the different                                                                                                                                                          |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | phases of abstraction refinement.                                                                                                                                                                      | 88  |

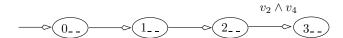

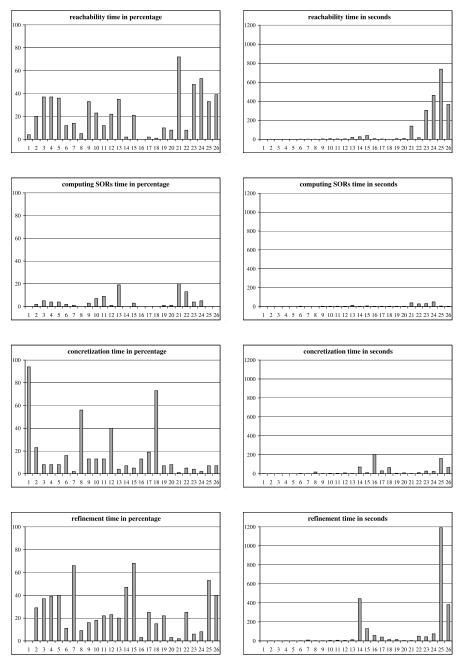

| 5.1  | Parallel composition of automata and its impact                                                                                                                                                        |     |

|      | on SCCs.                                                                                                                                                                                               | 96  |

| 5.2  | The generic SCC analysis algorithm D'N'C.                                                                                                                                                              | 97  |

| 5.3  | An example of using don't cares in the computation of SCCs.                                                                                                                                            | 100 |

| 5.4  | Another example of using don't cares in the computation of SCCs.                                                                                                                                       | 101 |

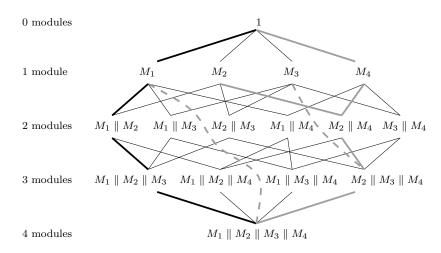

| 5.5  | Lattice of approximations.                                                                                                                                                                             | 103 |

| 5.6  | An SCC partition refinement tree.                                                                                                                                                                      | 105 |

| 6.1  | Guided search of fair cycles and sharp image.                                                                                                                                                          | 115 |

| 7.1  | The Far Side image computation algorithm.                                                                                                                                                              | 132 |

| 7.2  | Minimizing the transition relation.                                                                                                                                                                    | 133 |

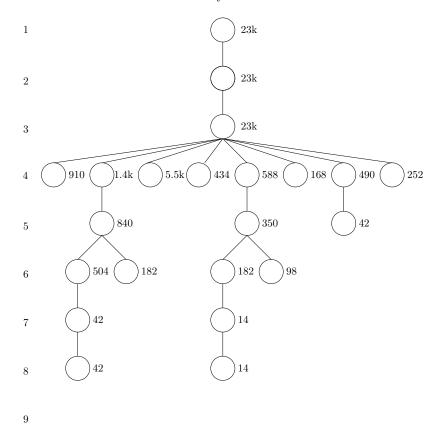

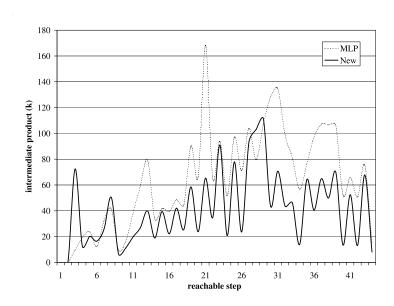

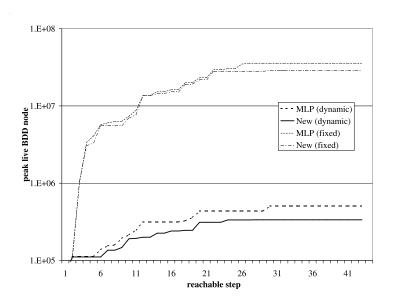

| 7.3  | s5378opt: The upper part is the BDD size of the intermediate products at different steps during the reachability analysis; the lower part is the total number of live BDD nodes, including BDDs repre- |     |

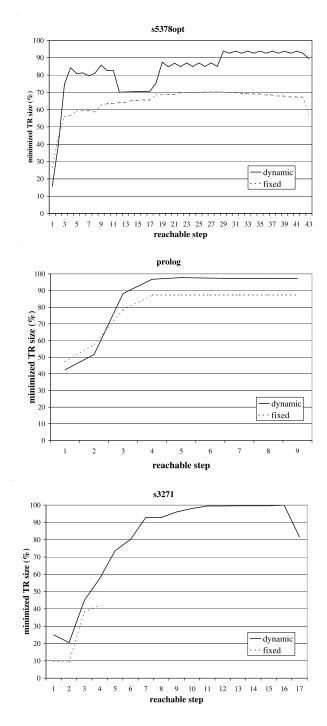

| 7.4  | senting the accumulated reachable states.  The BDD size reduction of the transition relation, in terms of the ratio of the BDD size of minimized                                                       | 140 |

|      | transition relation to the original BDD size.                                                                                                                                                          | 141 |

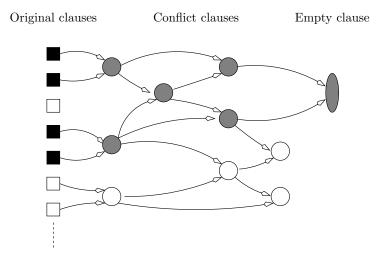

| 8.1  | Illustration of the resolution graph.                                                                                                                                                                  | 145 |

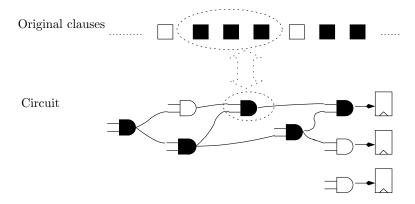

| 8.2  | From unsatisfiable cores to abstractions.                                                                                                                                                              | 146 |

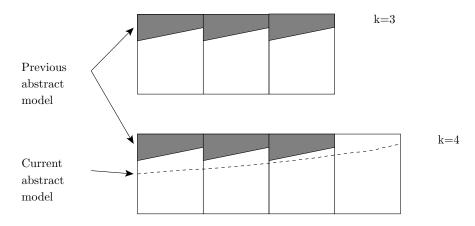

| 8.3  | Previous abstractions to help solving the current BMC instance.                                                                                                                                        | 148 |

| 8.4  | Refining the SAT decision order in bounded model checking.                                                                                                                                             | 150 |

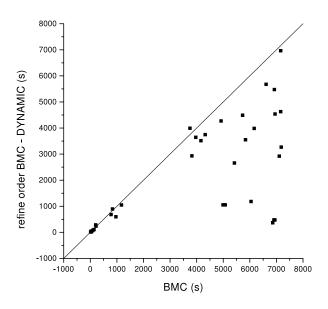

| 8.5  | Scatter plots: plain BMC vs. BMC with the refined ordering.                                                                                                                                            | 155 |

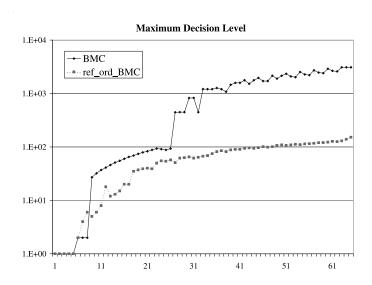

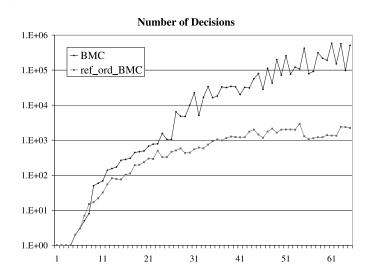

| 8.6  | Reduction of the size of decision trees.                                                                                                                                                               | 156 |

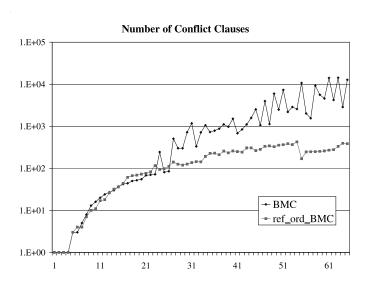

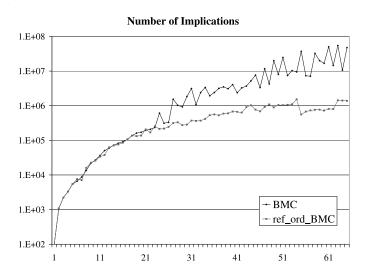

| 8.7  | Reduction of the number of conflicts and implications.                                                                                                                                                 | 157 |

|      |                                                                                                                                                                                                        |     |

# List of Tables

| 4.1 | Comparing invariant checking algorithms.                       | 85  |

|-----|----------------------------------------------------------------|-----|

| 4.2 | Correlation between the final proofs of GRAB and CA.           | 86  |

| 4.3 | Comparing Grab, +FineGrain, and +ARDC.                         | 87  |

| 6.1 | Comparing Emerson-Lei and D'n'C. With RDC's.                   | 123 |

| 6.2 | Comparing EL, D'n'C, and D'n'C <sup>#</sup> . With RDC's.      | 124 |

| 6.3 | Comparing EL, D'n'C, and D'n'C#. With ARDC's.                  | 125 |

| 6.4 | Comparing EL, D'n'C, and D'n'C <sup>#</sup> . With ARDC's.     | 126 |

| 7.1 | Comparing FarSideImg and MLP with dynamic variable reordering. | 137 |

| 7.2 | Comparing FarSideImg and MLP with fixed variable ordering.     | 138 |

| 8.1 | Comparing BMC with and without refining the                    |     |

|     | SAT decision order.                                            | 154 |

### **Preface**

This book summarizes our research work conducted in the University of Colorado at Boulder from 2000 to 2004 while the first author was pursuing his Ph.D. degree in the Department of Electrical and Computer Engineering. The Ph.D. dissertation won the 2003-2004 ACM Outstanding Ph.D. Dissertation Award in Electronic Design Automation. This ACM award, established by ACM SIGDA, is given each year to an outstanding Ph.D. dissertation that makes the most substantial contribution to the theory and/or application in the field of electronic design automation.

Our research addresses the problem of applying automatic abstraction refinement to the model checking of large scale digital systems. Model checking is a formal method for proving that a finite state transition system satisfies a user-defined specification. The primary obstacle to its widespread application is the capacity problem: the state-of-the-art model checker cannot directly handle most industrial-scale designs. Abstraction refinement, an iterative process of synthesizing a simplified model to help verifying the original model, is a promising solution to the capacity problem. In this book, several fully automatic abstraction refinement techniques are proposed to efficiently reach or come close to the simplest abstraction.

First, a fine-grain abstraction approach is proposed to keep the abstraction granularity small. With the advantage of including only the relevant information, the fine-grain abstraction is proved to be indispensable in verifying systems with complex combinational logics. A scalable game-based refinement algorithm called GRAB is proposed to identify the refinement variables based on the systematic analysis of all the shortest counterexamples. Compared to single counterexample guided refinement methods, this algorithm often produces a smaller abstract model that can prove or refute the same property.

Second, a compositional SCC analysis algorithm called DNC is proposed in the context of LTL model checking to quickly identify unimportant parts of the state space in previous abstractions and prune them away before verification is applied to the next abstraction level. With a speed-up of up to two orders of magnitude over standard symbolic fair cycle detection algorithms, DnC demonstrates the importance of reusing information learned from previous abstraction levels to help verification at the current level.

Finally, BDD based symbolic image computation and Boolean satisfiability check are revisited in the context of abstraction refinement. We propose two new algorithms in order to improve the computational efficiency of BDD based symbolic fixpoint computation and SAT based bounded model checking, by applying the idea of abstraction and successive refinements inside the two basic decision procedures.

Analytical and experimental studies demonstrate that the fully automatic abstraction refinement techniques proposed in this book are the key to applying model checking to large systems. The suite of fully automatic abstraction refinement algorithms has demonstrated significant practical importance. Some of these BDD and SAT based algorithms have been adopted by various commercial/in-house verification tools in industry.

CHAO WANG, GARY D. HACHTEL, FABIO SOMENZI

**April** 2006

## Chapter 1

#### INTRODUCTION

Our society is increasingly dependent on various electronic and computer systems. These systems are used in consumer electronics, automobiles, medical devices, traffic controllers, avionics, and space programs, etc. Many of these systems can be classified as critical systems—safetycritical, mission-critical, or cost-critical. Design errors in these critical systems are generally intolerable, since they either cost a lot of money, or cost lives. However, designing a flawless computer system is becoming harder as the size of the system keeps getting larger. In the hardware design community, for instance, functional verification has been identified as the bottleneck in the entire design process. According to ITRS (the International Technology Roadmap for Semiconductors [ITR03]), two thirds of a typical ASIC design budget goes into verification, and verification engineers frequently outnumber design engineers in large project teams. Still, over 60% of the IC designs require a second "spin" due to logic and functional level errors. Similar problems also exist in the software community, especially in the design and implementation of embedded and safety-related software systems (device drivers, air traffic control systems, security protocols, etc.). The vast majority of verification experts believe that formal analysis methods are indispensable in coping with this "verification crisis."

Traditional verification techniques are simulation and testing. Simulation is applied to a model of the product, while testing is applied to the product itself. The basic idea of simulation and testing is feeding in some test vectors and then checking the output for correctness. The disadvantage of this "trial-and-error" based approach is that all the possible input conditions must be checked in order to make sure the design is correct. However, even for pure combinational circuits, it is infeasi-

ble to enumerate all the possible input conditions except for very small designs. For sequential circuits, there can be an infinite number of input conditions due to the possibly unbounded number of time instances. Therefore, although simulation and testing are very useful in detecting "bugs" in the early stages of the design process, they are not suitable for certifying that the design meets the specification.

To get a mathematical proof that the design satisfies a given specification under all possible input conditions, one needs formal verification techniques. Model checking and theorem proving are two representatives of the existing formal verification techniques. Given a finite state model and a property expressed in temporal logics, a model checker can construct a formal proof when the model satisfies the property [CE81, QS81]. If the property fails, the model checker can show how it fails by generating a counterexample trace. Model checking is fully automatic in the sense that the construction of proof or refutation does not require the user's intervention. This is in contrast to the formal techniques based on theorem proving, which rely on the user's expertise in logics and deductive proof systems to complete the verification.

Model checking has been regarded as a potential solution to the "verification crisis" in the computer hardware design community. It is showing promise for many other applications as well, including real-time system verification [AHH96], parameterized system verification [EK03], and software verification [VB00, BMMR01, MPC<sup>+</sup>02].

The primary obstacle to the widespread application of model checking to real-world designs is the capacity problem. Since model checking uses an exhaustive search of the state space of the model to determine whether a specification is true or false, the complexity of model checking depends on the number of states of the model as well as the length of the specification. Due to its exponential dependence on the number of state variables or memory elements, the number of states of the model can be extremely large even for a moderate-size model. This is known as the state explosion problem. A major breakthrough in dealing with state explosion was symbolic model checking [BCM<sup>+</sup>90, McM94] based on Binary Decision Diagrams (BDDs [Bry86]). However, even with these symbolic techniques, the capacity of model checking remains limited: The state-of-the-art model checkers still cannot directly handle most industry-scale designs. In fact, symbolic model checkers often lose their robustness when the model has more than 200 binary state variables; at the same time, hardware systems become more and more complex because of Moore's law and the increasing use of high level hardware description languages (HDLs)—models with thousands or tens of thousands of state variables may vet look modest.

Introduction 3

#### 1.1 Background

Abstraction is an important technique to bridge the capacity gap between the model checker and large digital systems. When a system cannot be directly handled by the model checker, abstraction can be used to remove information that is irrelevant to the verification of the given property. We then build an abstract model which hopefully is much simpler and apply model checking to it. In doing so, an abstract interpretation [CC77], or a relation between the abstract system and the concrete system is created. For it to be useful in model checking, abstraction must preserve or at least partially preserve the property to be verified. There exist automatic abstraction techniques under which a certain subclass of temporal properties are preserved. For instance, bi-simulation based reduction [Mil71, DHWT91] preserves the entire propositional  $\mu$ calculus. However, property-preserving abstractions are either very hard to compute or do not achieve a drastic reduction [FV99], and therefore are less attractive in practice. A more practical approach is called property driven abstraction, which preserves or partially preserves only the property at hand. Along this line, Balarin et al. [BSV93], Long [Lon93], and Cho et al. [CHM<sup>+</sup>96a] have studied various ways of deriving an abstract model from the concrete system for model checking.

Abstraction refinement was introduced by Kurshan [Kur94] in the context of model checking linear properties specified as  $\omega$ -regular automata. In this paradigm, verification is viewed as an iterative process of synthesizing a simplified model that is sufficient to prove or refute the given property. In COSPAN [HHK96], the initial abstraction contains only the state variables in the property and leaves the other variables unconstrained. Since unconstrained variables can take arbitrary values, the abstract model is an over-approximation in the sense that it contains all possible execution traces of the original model, and possibly more. Therefore, when a linear time property holds in the abstract model, it also holds in the concrete model; when the property fails in the abstract model, however, the result is inconclusive. In the case of inconclusive result, the abstract model is refined by adding back some relevant but previously unconstrained variables. The key issue in abstraction refinement is to identify in advance which variable is relevant and which is not. Note that an over-approximated abstraction is applicable not only to linear properties specified as  $\omega$ -regular automata, but also to other universal properties including LTL [Pnu77] and ACTL [CE81, EH83], because over-approximation suffices to prove these properties true.

For practical reasons, it is important to keep the abstraction refinement process fully automatic. Manual abstraction techniques can be very powerful when they are carried out carefully by experienced users.

However, it often requires a significant amount of user's intervention and in-depth knowledge of the design. In fact, manual abstraction is very labor intensive and can be error-prone even for skilled users, making it hard for verification to keep up with the design schedule in real industry settings. Therefore, fully automated abstraction techniques are far more attractive in practice. In abstraction refinement, a procedure typically starts with a coarse initial abstraction and then automatically augments the abstract model by iterative refinement.

The main challenge in abstraction refinement is related to the ability of generating a final abstract model that is as simple as possible. The final abstraction, or deciding abstraction, is the one that decides the truth of the property to be verified. One can always start with a very coarse initial abstraction and keep refining it until the abstraction becomes deciding. Therefore, the effectiveness of the refinement algorithm is critical in keeping the final abstract model small. Existing refinement algorithms can be classified into the following categories. Some refinement algorithms rely on information about the structure of the model, e.g., the pair-wise latch relation [LPJ<sup>+</sup>96] or the variable dependency graph [LNA99]. Some refinement algorithms rely on the analysis of the set of approximate satisfying states of the given property produced in a previous model checking run, e.g., the operation-based refinement methods [PH98, JMH00]. Some refinement algorithms are driven by spurious abstraction counterexamples produced in a previous model checking run [CGJ<sup>+</sup>00, WHL<sup>+</sup>01, CGKS02, CCK<sup>+</sup>02, GKMH<sup>+</sup>03, MH04]; in these methods, the goal of refinement is to remove the abstract counterexamples that do not correspond to any real path in the concrete model. Other refinement algorithms rely on the analysis of unsuccessful bounded model checking runs [MA03, LWS03, GGYA03, LS04, LWS05, ZPH04, ZPHS05]. In the latter cases, unsatisfiability proofs of these bounded model checking instances directly induce abstract models that are sufficient for disabling all counterexamples of a certain length.

The simplicity of the final abstract model is bounded ultimately by the degree of locality of the given property in the model. In general, a high degree of locality is necessary for the success of abstraction refinement. For a property whose proof or refutation relies on detailed knowledge of the entire system, it is clear that abstraction refinement is ineffective. In practice, however, the properties used in model checking are often partial specifications of the system behavior, and user-specified properties tend to depend on only part of the system. This is largely due to the structured programming or design style adopted by engineers. In this case, it is the refinement algorithm's responsibility to exploit fully the degree of locality of a given property. To measure the quality of dif-

Introduction 5

ferent abstraction refinement algorithms, we define an important metric called  $abstraction\ efficiency$  as follows:

$$\eta = \left(1 - \frac{\text{final abstract model size}}{\text{original model size}}\right).$$

For every pair of model M and property  $\phi$ , there exists an optimum or maximum abstraction efficiency  $\eta^*$ . Note that  $\eta^*$  is a property of the specific verification problem  $\langle M, \phi \rangle$ , not a property of the abstraction refinement algorithm. As a heuristic principle, the closer to the optimum value it can achieves, the better a certain abstraction refinement algorithm is.

Another important metric for abstraction refinement is the *rate of convergence*. This characterizes how quickly a refinement algorithm converges from the initial abstract model to a deciding abstraction. In practice, this can be measured either by the number of refinement iterations or by the overall run time. We have observed cases for which some algorithms converge quickly to a near optimal abstraction while other algorithms spend a lot of time searching in vain for such an abstraction. In the ideal case, an algorithm should find, at each abstraction refinement iteration, a set of refinement variables that is a subset of an optimum deciding abstraction.

#### 1.2 Our Contributions

This book deals with the main challenge in abstraction refinement, i.e., the ability to efficiently reach or come close to the optimum deciding abstraction. We propose several fully automatic abstraction techniques in order to improve the overall computation efficiency as well as the rate of convergence. Together, they address the following three problems that are critical in the abstraction refinement loop:

- 1 How to make the abstraction more concise?

- 2 How to identify and reuse critical information from previous abstraction levels?

- 3 How to make the basic decision procedures used in abstraction refinement more efficient?

In order to achieve a higher abstraction efficiency, it is crucial to keep the refinement granularity small so that only the relevant information is included in the abstract model. That is, each successive refinement should include only variables that are present in an optimal or near-optimal deciding abstraction. In previous work, the abstraction granularity is often limited at the state variable level: the entire fanin combinational logic cone of a state variable is either included in or completely excluded from the abstract model. However, it is often the case that not every one of these fan-in logic gates is necessary for the verification of a certain property, even if the state variable itself is indeed necessary. Including these redundant logic gates often significantly increases the complexity of the abstract model—an abstract model with few state variables may end up containing a large number of logic gates.

In this book, we propose a fine-grain abstraction approach to push the granularity of abstraction beyond the usual state variable level. Boolean network variables are selectively inserted into large combinational logic cones to partition them into smaller pieces. In the abstraction as well as the successive refinements, Boolean network variables are given the same status as state variables—both are considered as atoms. With this approach, refinement strategies must search a two-dimensional space. Refinement in the sequential direction is comprised of the addition of new state variables only, which is typical of much of the prior art [LPJ<sup>+</sup>96, JMH00, CGJ<sup>+</sup>00, CGKS02]. Refinement in the *Boolean* direction is comprised of the addition of Boolean network variables only, which does not increase the number of abstract states but refines the transition relation among them. Although cut-set variables that are similar to Boolean network variables were used in the previous work of Wang et al. [WHL<sup>+</sup>01] and Glusman et al. [GKMH<sup>+</sup>03], these variables were not treated the same as state variables during refinement. We shall show that by separating the two refinement directions and carefully controlling the direction at each iteration, we can produce refinement variable sets that are significantly more concise.

Spurious counterexamples in an abstract model have been used in previous work to compute the set of refinement variables. With the exception of [GKMH<sup>+</sup>03], the prior art of counterexample based refinement relies exclusively on a single counterexample. In practice, however, there can be an extremely large number of spurious counterexamples when the property fails. In that case, arbitrarily picking up one counterexample and use it to drive the refinement is "a-needle-in-the-haystack" approach. In this book, we present a way to capture, for invariant properties, all the shortest counterexamples using a data structure called the Synchronous Onion Rings (SORs). A new refinement algorithm, called GRAB, is proposed to identify the refinement variables by systematically analyzing all the shortest counterexamples. GRAB has two novel features: First, it takes a generation of refinement steps to systematically eliminate all spurious counterexamples supported by a given set of SORs. Second, each refinement step in the current generation is computed using a scal-

Introduction 7

able game-based strategy that depends solely on the current abstract model. Note that being able to compute the refinement without using the concrete model is crucial to the scalability of the algorithm, since the working assumption is that the concrete model is large and any computation on it is prohibitively expensive. In contrast, previous refinement methods in [CGJ<sup>+</sup>00, CGKS02, CCK<sup>+</sup>02] do not scale well, because they rely on computation in the concrete model.

Due to the global guidance from the SORs, and the quality and scalability of the game-based variable selection computation, GRAB demonstrates significantly advantages over these previous refinement algorithms – it can solve significantly larger problems, require less memory and less CPU time. Although the method in [GKMH<sup>+</sup>03] is also driven by multiple counterexamples, it does not guarantee to capture each and every one of the shortest counterexamples. As a result, this refinement method is often less accurate than the SOR based refinement and is incapable of catching concretizable counterexamples at the earliest possible refinement step.

Proof based abstraction methods in [MA03, LWS03, GGYA03, LS04, LWS05, ZPH04, ZPHS05] captures implicitly all the shortest counterexamples. However, these are SAT based methods and rely on a SAT solver to produce the unsatisfiability proof of a SAT instance in the concrete model. In contrast, our core refinement variable selection algorithm is pure BDD based, even though we use SAT as well in concretization test and in predicting the refinement direction. We note that a small unsatisfiability proof, i.e., the one with a small subset of Boolean variables or clauses, does not automatically give a small refinement set [LS04, GGA05]. Both proof-based and counterexample based methods have their own advantages and disadvantages. A detailed experimental comparison of GRAB with a proof-based refinement algorithm can be found in [LWS05], showing that these two methods complement each other on the various test cases. Amla et al. [ADK<sup>+</sup>05] also published results of their experimental evaluation of the various SAT based abstraction methods. There is also a trend of combining counterexample based methods and proof-based methods in abstraction refinement [AM04].

In abstraction refinement, we need to model check the abstract model repeatedly while it is gradually refined. Information gathered at previous abstraction levels can be carried on and be used to speed up the verification at the current level. In this book, we propose a compositional SCC (Strongly Connected Component) analysis algorithm, called DNC, to quickly identify unimportant parts of the state space and prune them away before going to the next abstraction. The search state space is also

disjunctively decomposed into smaller subspaces that can be checked in isolation. Although there exist several symbolic SCC algorithms in the prior art [HTKB92, XB00, BGS00, GPP03] and some of them have been applied to model checking [FFK<sup>+</sup>01, SRB02], these methods are not compositional, and would not be effective on the larger practical examples studied in this book. In this book, we also prove that the strength of an SCC or a set of SCCs decreases monotonically with refinement, which allows the model checking algorithm to tailor the proof to the strength of the SCC at hand. The concept of automaton strength was due to Kupferman and Vardi [KV98] and Bloem et al. [BRS99]. Although the strength of the automaton was used in [BRS99] to improve LTL model checking, we believe that DNC is the first to systematically exploit this important property in the context of abstraction refinement.

The idea of abstraction followed by the successive refinements is also applied to the two basic decision procedures used in model checking: BDD based symbolic image computation and Boolean Satisfiability (SAT) check. Image computation [CBM89a, GB94] accounts for most of the CPU time in BDD based symbolic model checking. The peak sizes of the BDDs produced during the computation are essential in determining whether or how fast image computation can be completed on a given computer. In this book, we propose a novel image computation algorithm called FARSIDE image, to reduce the peak BDD size inside image computation by minimizing the transition relation with over-approximated images as care sets. Exact and approximate reachable states have been widely used to improve image computation since the early work of Ranjan et al. [RAB+95] and Moon et al. [MJH+98]. However, BDD minimization was effective only when being applied to the near side, or present-state variables of the transition relation. The FARSIDE image algorithm is the first to achieve a significant performance gain by applying BDD minimization to the far side, or next-state variables of the transition relation. It may seem surprising that significant improvements to the low level BDD work routines can be obtained long after the time when BDD methods were a consistent focus in the relevant conferences and journals. From our discussion and presented results, it should be clear that these improvements are obtained only when compositional methods are applied to models that are much larger than previously considered.

Deciding the SAT problem of a Boolean formula is a fundamental computation in Bounded Model Checking (BMC [BCCZ99]). In BMC, we search for counterexamples of a finite length in the given model, and the existence of a finite-length counterexample is formulated into a Boolean formula that is satisfiable if and only if a counterexample exists. When

Introduction 9

the Davis-Longeman-Loveland recursive search procedure [DLL62] (implemented in many modern SAT solvers) is used to solve the SAT problem, the variable decision ordering affects the performance significantly. In this book, we propose a new algorithm to compute a good variable decision order for the series of SAT problems in BMC. The new algorithm exploits the fact that the SAT problems in BMC are highly correlated, and therefore information learned from previous problems can help solving the current problem. The new variable ordering is computed based on the analysis of the unsatisfiability proofs of previous SAT instances, and is gradually refined as the BMC unrolling depth keeps increasing. Shtrichman also studied in [Sht00] the use of static ordering to improve the SAT search in BMC. However, his method is based primarily on the unrolled circuit structure, and therefore is completely orthogonal to ours. Due to the strong correlation among different SAT instances in BMC, applying our new decision ordering can significantly reduce the sizes of the SAT search trees and therefore improve the overall performance of BMC.

To summarize, all the new techniques proposed in this book are fully automatic and are crucial at improving the performance of abstraction refinement. Their application to model checking can significantly increase the model checker's ability to handle large designs. Our experimental studies on real-world benchmark circuits indicate that these automatic abstraction refinement techniques are the key to applying model checking to industrial-scale systems.

#### 1.3 Organization of This Book

This book has nine chapters. Chapter 2 is an introduction to the basic concepts and notations commonly used in model checking, including finite state models, temporal logics, Büchi automata, symbolic model checking, bounded model checking, and abstraction refinement. This chapter should be an easy reading for those who are familiar with model checking. We have also tried to make the materials easily accessible to readers who are in the general areas of computer science but not very familiar with model checking. From Chapter 3 to Chapter 8, we present our main research contributions in details.

In Chapter 3, we introduce the notion of abstraction granularity and present the Fine-Grain abstraction approach. We use the simulation relation between the abstract and concrete models to explain why model checking of the abstract system may be conservative. We present the data structure of the SORs to capture all the shortest abstract counterexamples. We show how to use SAT based multi-thread concretization test to decide whether the abstract counterexamples are real or not.

In Chapter 4, we present the GRAB refinement algorithm for selecting refinement variables based on a two-player reachability game in the abstract model. At each refinement iteration, we show how to decide the appropriate refinement direction using a SAT check. In both refinement directions, a greedy generational minimization is used at the end to remove redundant refinement variables. Finally, we discuss the use of sequential don't cares to constrain the behavior of the abstract model.

In Chapters 5 and 6, we address the important problem of carrying on information from previous abstraction levels to the current level, and applying it to speed up model checking. We present a compositional SCC analysis algorithm called DNC for model checking LTL properties. Information learned from previous abstraction levels is used to restrict the search for fair cycles at the current abstraction level. We will explain the use of SCC strength reduction, disjunctive state space decomposition, and guided search for fair cycles in the general framework of abstraction refinement.

In Chapters 7 and 8, we apply the idea of abstraction and successive refinements to the basic symbolic computation algorithms in model checking. In Chapter 7, we focus on improving the performance of BDD based symbolic image computation and present the FARSIDE image computation algorithm. In Chapter 8, we discuss the variable decision ordering of a SAT solver based on the DLL procedure in the context of bounded model checking. We then present a new variable ordering algorithm to improve the performance of the SAT checks in BMC. In both chapters, we conduct experiments to demonstrate the effectiveness of the proposed techniques.

We conclude in Chapter 9 and point out some interesting research directions.

## Chapter 2

#### SYMBOLIC MODEL CHECKING

Model checking [CE81, QS81] is an algorithmic method for proving that a digital system satisfies a user-defined specification. Both the system and the specification must be formally specified: The model of the system must have a finite number of states; the specification, or property, is often expressed in temporal logics. In the model checking literature, the model and the property are often represented by the Kripke structure and a temporal logic formula, respectively.

Given a model K and a property  $\phi$ , model checking is used to check whether K models  $\phi$ , denoted by  $K \models \phi$ . For properties specified in Computational Tree Logic (CTL [CE81, EH83]), the model checking problem can be solved by a set of least and/or greatest fixpoint computations [CES86]. For properties specified in Linear Time Logic (LTL [Pnu77]), model checking is often transformed into language emptiness checking in a generalized Büchi automaton. In this automatatheoretic approach [VW86], the negation of the given LTL formula is encoded into a Büchi automaton, which is then composed with the model. The LTL model checking problem is then decided by checking the language of the composed system—the model satisfies the property if and only if the language of the composed system is empty. Therefore, the underlying LTL model checking algorithms are usually variants of algorithms for computing Strongly-Connected Components (SCCs).

In this chapter, we first introduce the basic concepts and notations commonly used in model checking. We then review some of the fundamental algorithms in symbolic model checking, which includes BDD based symbolic fixpoint computation, SCC hull and SCC enumeration algorithms, SAT and bounded model checking, and iterative abstraction refinement.

#### 2.1 Finite State Model

In model checking, we deal with a formal model of the given digital system, known as the Kripke structure. A Kripke structure is an annotated finite-state transition graph.

Definition 2.1 A Kripke structure is a 5-tuple

$$K = \langle S, S_0, T, A, \Lambda \rangle$$

,

where S is a finite set of states,  $S_0 \subseteq S$  is the set of initial states,  $T \subseteq S \times S$  is the transition relation, A is a finite alphabet for which a set P of atomic propositions is given and  $A = 2^P$ , and  $\Lambda : S \to A$  is the labeling function.

We further require that the transition relation of a Kripke structure be complete; that is, every state has at least one successor. With this assumption, we can extend any finite state path in the state transition graph into an infinite one.

As the standard representation of models in the model checking literature, the Kripke structure has its origin in modal logic, the generalization of temporal logic. In modal logic, a certain formula is interpreted with respect to a state inside a universe, a domain of discourse, and a relation establishing how the validity of a predicate changes from state to state. Temporal logic is a special case of modal logic that allows us to reason about how predicates evolve over time. In temporal logic model checking, a node or state of the Kripke structure represents the "state" of the given system at a certain time, and the change from state to state represents a time change.

From an engineer's point of view, the Kripke structure is nothing but a labeled finite state machine (FSM). The additional features, i.e., the finite alphabet and a labeling function from states to sets of atomic propositions, make it possible to specify simple propositional properties on the finite state machine. These propositional properties, combined with some temporal operators, allow us to specify properties like " $\neg abort$  holds on all the states reachable from the initial states" or "from a state labeled req we will eventually reach a state labeled ack." We will introduce temporal logic operators in the next section. Now let us focus on propositional properties and take a look at the example FSM at the right-hand side of Figure 2.1.

The FSM in Figure 2.1 has four states, among which three are reachable from the single initial state a. Propositions p and q belong to the finite alphabet. With the labeling function and initial predicate indicated in Figure 2.1, the finite state machine is augmented into a Kripke

Figure 2.1. An example of the Kripke structure.

structure defined as follows:

$$\begin{array}{llll} S & = & \{a,b,c,d\} & & \Lambda(a) & = & \{p\} \\ S_0 & = & \{a\} & & \Lambda(b) & = & \{\,\} \\ T & = & \{(a,a),(a,b),(b,c),(c,c),(d,d),(d,a)\} & & \Lambda(c) & = & \{p\} \\ P & = & \{p,q\} & & \Lambda(d) & = & \{q\} \end{array}$$

Given a sequential circuit, the construction of the finite state machine from the system description is straightforward. A digital circuit is often defined as an entity with memory elements (latches and flip-flops), combinational logic gates, input signals, and internal wires. The transition functions of the memory elements are defined in terms of the current values of these memory elements and the input signals.

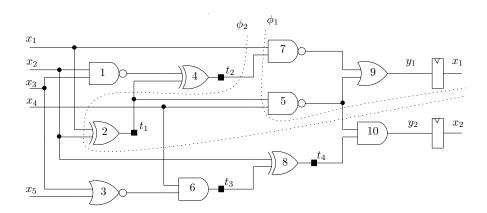

Figure 2.2 gives an example circuit, in which we use the variables  $x_1$  and  $x_0$  to represent the outputs of the two registers, and variables  $y_1$  and  $y_0$  to represent their data inputs. Note that after a clock cycle, the values of  $y_1$  and  $y_0$  will be propagated to the register outputs. Therefore, we often call  $x_1$  and  $x_0$  the present-state (or current-state) variables, and call  $y_1$  and  $y_0$  the next-state variables. In this example, we use the variable  $w_0$  to represent the value of a primary input signal.

States in the corresponding FSM are mapped to the different valuations of the set of memory elements. Edges in the state transition graph correspond to the changes of states among different clock cycles. For the example in Figure 2.2, we can write out the transition functions of the

Figure 2.2. A sequential circuit example.

two registers as

$y_1: \neg x_1 \wedge x_0 \vee x_1 \wedge \neg x_0 \vee x_1 \wedge x_0 \wedge \neg w_0$  $y_0: \neg x_1 \wedge \neg x_0 \wedge w_0 \vee x_1 \wedge x_0 \wedge \neg w_0$

Given the values of present-state variables and the input signal, the values of next-state variables are determined by their transition functions. When the current values of the two registers are  $(x_1 = 0, x_0 = 0)$ , for instance, their values at the next clock cycle will be  $(y_1 = 0, y_0 = 0)$  for  $w_0 = 0$ , and  $(y_1 = 0, y_0 = 1)$  for  $w_0 = 1$ . If we use the state encoding scheme and labeling functions described on the left-hand side of Figure 2.1, we will get the right-hand side Kripke structure in the same figure.

Since the number of memory elements in a sequential circuit is finite, there are only a finite number of states. However, There is a well-known  $state\ explosion$  problem. The total number of states in the FSM can be as large as  $2^n$  for a system with n binary state variables. Due to its exponential dependence on the number of state variables, the number of states of the model can be extremely large even for a moderate-size system.

Some digital systems may have an infinite number of states. Software with recursive function calls and unbounded data structures, for instance, fall into this category. Other examples include timed systems and hybrid systems [ACH<sup>+</sup>95, AH96], in which the state variables can be of unbounded integer or even real type. Since model checking requires the Kripke structure to be finite-state, before we can apply model

checking, a certain degree of abstraction is needed to extract suitable verification models from these systems. In general, abstraction used for this purpose is either under-approximation or over-approximation. The process of mapping an infinite state space into a finite state space, by itself, is an important research topic, and is beyond the scope of this book. In the sequel, we assume that the finite state model of a given system, or the Kripke structure, is already available.

#### 2.2 Temporal Logic Property

Propositional logic is the basis for specifying properties. A proposition is a declarative sentence about the Kripke structure that is either true or false. Propositions are represented by a set of propositional variables  $p, q, \ldots$  plus the truth values true and false. A formula consisting of a propositional variable is called an *atomic proposition*. The evaluation of an atomic proposition maps to a set of states in the Kripke structure.

Propositional logic formulae are defined in terms of atomic propositions with the common logical connectives.

Definition 2.2 A propositional logic formula is defined as follows:

- atomic propositions are propositional formulae;

- if  $\phi$  is a propositional formula, then  $\neg \phi$  is a propositional formula;

- if  $\phi$  and  $\psi$  are propositional formulae, then  $\phi \wedge \psi$ ,  $\phi \vee \psi$ ,  $\phi \rightarrow \psi$ ,  $\phi \leftrightarrow \psi$  are propositional formulae.

In the set of logical connectives, the unary operator negation  $(\neg)$  and the binary operation logical AND  $(\land)$  constitute a minimal subset that is sufficient for defining propositional logic. Besides  $\land$ , there are 15 other binary logical connectives; however, all of them can be expressed in terms of  $\neg$  and  $\land$ . For example, under the De Morgan's law the formula  $\phi \lor \psi$  can be rewritten into  $\neg(\neg\phi \land \neg\psi)$ . The "implies" operator  $\rightarrow$  means "only if", and therefore  $\phi \to \psi$  is equivalent to  $\neg\phi \lor \psi$ . Similarly, the formula  $\phi \leftrightarrow \psi$  is equivalent to  $\neg\phi \land \neg\psi \lor \phi \land \psi$ .

Propositional logic is incapable of reasoning about the evolution of valuations over time. When the truth of a property depends on not only the present valuation, but also on the valuations in the past or in the future, we need temporal logics. The most common temporal logics to express system properties are Computational Tree Logic (CTL) and Linear Time Temporal Logic (LTL). CTL and LTL are subsets of the more general CTL\*. In this book, we will focus on Linear Time Temporal Logic, but we will also briefly describe the Computational Tree Logic, since some of its operators will be used in our discussion of model checking algorithms.

There are two very different ways of modeling time in temporal logics. The linear time model assumes that each time instance has exactly one successor; the branching time model, on the other hand, allows several successors for each time instance. LTL is based on the linear time model. LTL formulae specify properties about the future of each individual execution trace such as the condition ack will eventually be true, or that the condition busy will be true until another condition done becomes

true. Logics based on the branching time model, such as CTL, deal with all possible execution traces. CTL formulae can specify properties such as that if the condition reset is true then on all paths the condition reset\_done will eventually be true.

LTL formulae are defined in terms of atomic propositions, the usual logic connectives, as well as linear time temporal operators. The two basic temporal operators in LTL are X and U, called *next* and *until*, respectively. The first operator is unary and the second is binary. The formula X $\phi$  means that  $\phi$  holds at the next point of time. The formula  $\phi$  U $\psi$  means that  $\phi$  has to hold until  $\psi$  becomes true, and  $\psi$  will eventually become true.

DEFINITION 2.3 A Linear Time Temporal Logic (LTL) formula is defined recursively as follows:

- atomic propositions are LTL formulae;

- if  $\phi$  and  $\psi$  are LTL formulae, so are  $\neg \phi$ ,  $\phi \land \psi$ , and  $\phi \lor \psi$ ;

- if  $\phi$  and  $\psi$  are LTL formulae, so are  $X \phi$  and  $\phi U \psi$ ;

Besides X and U, there are other temporal operators including G for globally, F for finally, and R for release. The formula  $G \phi$  means that  $\phi$  has to hold forever. The formula  $F \phi$  means that  $\phi$  will eventually be true. The formula  $\phi R \psi$  means that  $\psi$  remains true before the first time  $\phi$  becomes true (or forever if  $\phi$  remains false). These three temporal operators can be expressed in terms of the two basic ones:

$$\begin{array}{rcl} \mathsf{F}\,\phi &=& \mathsf{true}\,\mathsf{U}\,\phi \\ \mathsf{G}\,\phi &=& \neg\,\mathsf{F}\,\neg\phi \\ \phi\,\mathsf{R}\,\psi &=& \neg(\neg\psi\,\mathsf{U}\,\neg\phi) \end{array}$$

The semantics of LTL formulae are defined for an infinite path  $\pi = (s_0, s_1, ...)$  of the Kripke structure, where  $s_i \in S$  is a state,  $s_0$  is an initial state, and  $T(s_i, s_{i+1})$  evaluates to true for all  $i \geq 0$ . The suffix of  $\pi$  starting from the state  $s_i$  is represented by  $\pi^i$ . We use  $K, \pi^i \models \phi$  to represent the fact that  $\phi$  holds in a suffix of path  $\pi$  of the Kripke structure K. The property  $\phi$  holds for the entire path  $\pi$  if and only if  $K, \pi^0 \models \phi$ . When the context is clear, we will omit K and rewrite  $K, \pi^i \models \phi$  into  $\pi^i \models \phi$ . The semantics of LTL formulae are defined

recursively as follows:

```

\begin{array}{lll} \pi \models \mathsf{true} & \mathsf{always \ holds} \\ \pi \models \varphi & \mathsf{iff} \ \pi^0 \models \varphi \\ \pi \models \neg \varphi & \mathsf{iff} \ \pi \not\models \varphi \\ \pi \models \varphi \land \psi & \mathsf{iff} \ \pi \models \varphi \ \mathsf{and} \ \pi \models \psi \\ \pi \models \mathsf{X} \ \varphi & \mathsf{iff} \ \pi^1 \models \varphi \\ \pi \models \varphi \ \mathsf{U} \ \psi & \mathsf{iff} \ \exists i \geq 0 \ \mathsf{such \ that} \ \pi^i \models \psi \ \mathsf{and \ for \ all} \ 0 \leq j < i \ , \\ \pi^j \models \varphi \\ \pi \models \varphi \ \mathsf{R} \ \psi & \mathsf{iff \ for \ all} \ i \geq 0, \ \pi^i \models \psi; \ \mathsf{or} \ \exists j \geq 0 \ \mathsf{such \ that} \\ \pi^j \models \varphi \ \mathsf{and \ for \ all} \ 0 \leq i \leq j, \ \pi^i \models \psi \end{array}

```

The Kripke structure K satisfies an LTL formula  $\phi$  if and only if all paths from the initial states do. This means that all LTL properties are universal properties in the sense that we can add the path quantifier A as a prefix without changing the meaning of the properties. That is,  $K \models \phi$  is equivalent to  $K \models \mathsf{A}\,\phi$ , where the path quantifier A means  $\phi$  holds for all computation paths. Another path quantifier is E, which stands for there exists a computation path. E is not used in LTL, but both A and E are used in CTL.

An LTL formula is in the normal form if negation appears only in front of propositional formulae. For instance, the formula  $\mathsf{F} \neg \mathsf{F} p$  is not in the normal form since negation is ahead of the temporal operator  $\mathsf{F}$ ; on the other hand, the equivalent formula  $\mathsf{F} \mathsf{G} \neg p$  is in the normal form. We can always rewrite an LTL formula into normal form by pushing negation inside temporal operators. The following rules can be applied during the rewriting:

$$\begin{array}{rcl} \mathsf{X}\, p &=& \neg\,\mathsf{X}\,\neg p \\ \mathsf{G}\, p &=& \neg\,\mathsf{F}\,\neg p \\ p\,\mathsf{U}\, q &=& \neg(\neg q\,\mathsf{R}\,\neg p) \\ \mathsf{F}\, p &=& \mathsf{true}\,\mathsf{U}\, p \end{array}$$

Since an LTL formula  $\phi$  is a universal property and is equivalent to  $A \phi$ , the negation of  $\phi$  should be the existential property  $E \neg \phi$ .

The two path quantifiers are an integral part of Computational Tree Logic (CTL), and are used explicitly to specify properties related to execution traces in the computation tree structure. A (for all computation paths) specifies that all paths starting from a given state satisfy a property; E (for some computation paths) specifies that some of these paths satisfy a property.

DEFINITION 2.4 A Computational Tree Logic (CTL) formula is defined recursively as follows:

- atomic propositions are CTL formulae;

- if  $\varphi$  and  $\psi$  are CTL formulae, then  $\neg \varphi$ ,  $\varphi \wedge \psi$ , and  $\varphi \vee \psi$  are CTL formulae;

- if  $\varphi$  and  $\psi$  are CTL formulae, then  $\mathsf{EX}\,\varphi$ ,  $\mathsf{E}\,\psi\,\mathsf{U}\,\varphi$ , and  $\mathsf{EG}\,\varphi$  are CTL formulae.

A CTL formula is in the normal form if negation appears only in front of propositional formulae. Formula  $\neg \mathsf{AX}\, p$  is not in the normal form since negation is ahead of the temporal operator  $\mathsf{AX}$ ; on the other hand, the equivalent formula  $\mathsf{EX}\, \neg p$  is in the normal form. We can always rewrite a CTL formula into normal form by pushing negation inside temporal operators. The following rewriting rules can be applied during normalization:

$$\begin{array}{rcl} \mathsf{AX}\,p &=& \neg\,\mathsf{EX}\,\neg p \\ \mathsf{AG}\,p &=& \neg\,\mathsf{EF}\,\neg p \\ \mathsf{A}\,p\,\mathsf{U}\,q &=& \neg(\mathsf{E}\,\neg q\,\mathsf{U}\,\neg p\,\wedge\,\neg q)\,\wedge\,\neg\,\mathsf{EG}\,\neg q \\ \mathsf{AF}\,p &=& \mathsf{A}\,\mathsf{true}\,\mathsf{U}\,p \\ \mathsf{EF}\,p &=& \mathsf{E}\,\mathsf{true}\,\mathsf{U}\,p \end{array}$$

Many interesting properties in practice can be expressed in both LTL and CTL. However, there are also properties that can be expressed in one but not the other. The difference between an LTL formula and a CTL formula can be very subtle. For instance, the LTL formula  $\mathsf{FG}\,p$  holds in the Kripke structure in Figure 2.3, but the CTL formula  $\mathsf{AF}\,\mathsf{AG}\,p$  fails. (In the Kripke structure, p and q are state labels.)

Figure 2.3. A Kripke structure and its computation tree.

The reason is that the LTL property is related to the individual paths, and on any infinite path of the given Kripke structure we can reach the

state c from which p will holds forever. The CTL formula AFAGp, on the other hand, requires that on all paths from the state a we can reach a state satisfying AGp. Note that the only state satisfying AGp is the state c; however, the Kripke structure does not satisfy AF $\{c\}$ —as shown in the right-hand side of the figure, the left most path of the computation tree is a counterexample. On this particular path, we can stay in the state a while reserving the possibility of going to the state b (where p does not hold). Therefore, FGp and AFAGp represent two very similar but different properties.

The above example shows that LTL and CTL have different expressing powers. Some LTL properties, like  $\mathsf{FG}\,p$ , cannot be expressed in CTL. There are also CTL properties that cannot be expressed in LTL; an example in this category would be  $\mathsf{AGEF}\,p$ . Both LTL and CTL are strict subsets of the more general CTL\* logic [EH83, EL87]. The relationship among LTL, CTL, and CTL\* is given in Figure 2.4. In this book, we focus primarily on LTL model checking. Readers who are interested in CTL model checking are referred to [CES86, McM94] or the book [CGP99].

Figure 2.4. The relationship among LTL, CTL, and CTL\*.

We have used the term *universal property* during previous discussions. Now we give a formal definition of universal and existential properties.

DEFINITION 2.5 A property  $\phi$  is a universal property if removing edges from the state transition graph of the Kripke structure does not reduce the set of states satisfying  $\phi$ . A property  $\psi$  is an existential property if adding edges into the state transition graph of the Kripke structure does not reduce the set of states satisfying  $\psi$ .

It follows that all LTL properties and ACTL (the universal fragment of CTL) properties are universal. The existential fragment of CTL, or ECTL, is existential. For the propositional  $\mu$ -calculus formulae, those that do not use EX and EY in their normal forms are universal.

Temporal logic properties can also be classified into the following two categories: safety properties and liveness properties. The notion of safety and liveness was introduced first by Lamport [Lam77]. Alpern and Schneider [AS85] later gave a formal definition of both safety and liveness properties. Informally, a safety property states that something bad will not happen during a system execution. Liveness properties are dual to safety properties, expressing that eventually something good must happen. The distinction of safety and liveness properties was originally motivated by the different techniques for proving them.

We can think of a property as a set of execution sequences, each of which is an infinite sequence of states of the Kripke structure. A property is called a safety property if and only if each execution violating the property has a finite prefix violating that property. In other words, a finite prefix of an execution violating the property (bad thing) is irremediable no matter how the prefix is extended to a infinite path. Safety properties can be falsified in a finite initial part of the execution, although proving them requires the traversal of the entire set of reachable states. The invariant property  $\mathsf{G}\,p$  or  $\mathsf{AG}\,p$ , which states that the propositional formula p always holds, is a safety property. Other safety properties include mutual exclusion, deadlock freedom, etc.

A property is a liveness property if and only if it contains at least one good continuation for every finite prefix. This corresponds to the intuition that it is still possible for the property to hold (good thing to happen) after any finite execution. Liveness properties do not have a finite counterexample, and therefore in principle cannot be falsified after a finite number of execution steps. An example of liveness property is  $\mathsf{G}(p \to \mathsf{F}\,q)$ , which states that whenever the propositional formula p is true, the propositional formula p must become true at some future cycle although there is no upper limit on the time by which p is required to become true. Other liveness properties include accessibility, absence of starvation, etc.

#### 2.3 Generalized Büchi Automaton

An LTL formula  $\phi$  always corresponds to a Büchi automaton  $\mathcal{A}_{\phi}$  that recognizes all its satisfying infinite paths. In other words, the Büchi automation  $\mathcal{A}_{\phi}$  contains all the logic models of the formula  $\phi$ . If we consider the Kripke structure as a language generator and the Büchi automaton  $\mathcal{A}_{\phi}$  as a language recognizer, then we have  $K \models \phi$  if and only if all infinite words generated by K are accepted by  $\mathcal{A}_{\phi}$ . Therefore, the LTL model checking problem can be translated to  $\omega$ -regular language containment checking. Since checking language containment between two Büchi automata in general is PSPACE-complete [Kur94], it follows that LTL model checking is PSPACE-complete.

In practice, however, LTL model checking is often translated into language emptiness checking in a generalized Büchi automaton. This automata-theoretic approach [VW86] consists of the following three steps:

- 1 we negate the given property  $\phi$  and translate it into a Büchi automaton  $\mathcal{A}_{\neg\phi}$ , which accepts all the infinite paths that do not satisfy  $\phi$ ;

- 2 we then compose the model K and the property automaton  $\mathcal{A}_{\neg\phi}$  together. The system produced by parallel composition, denoted by  $(K||\mathcal{A}_{\neg\phi})$ , consists of only those infinite paths of K that are accepted by  $\mathcal{A}_{\neg\phi}$ ;

- 3 finally, we check whether the language of the composed system is empty.

If the language is empty, then  $K \models \phi$  since no infinite path in K is accepted by  $\mathcal{A}_{\neg \phi}$ . If the language is not empty, any accepting run in the composed system serves as a counterexample to  $K \models \phi$ .

LTL model checking via language emptiness has the same worst-case complexity bound as the language containment based approach, which is linear in the number of states of the model, but exponential in the length of the LTL formula. The exponential blow-up comes from the translation from LTL formulae to Büchi automata. However, this is often acceptable in practice, because user specified LTL formulae are usually small compared to the size of the model.

In the automata-theoretic approach, we can use the labeled generalized Büchi automata as a unified representation for the model K, the property automaton  $\mathcal{A}_{\neg\phi}$ , as well as the composed system $(K||\mathcal{A}_{\neg\phi})$ . A labeled generalized Büchi automaton is simply a Kripke structure augmented by a set of acceptance conditions. In other words, we can view

the model K as a special case of the labeled generalized Büchi automaton whose only acceptance condition is satisfied by all paths.

Definition 2.6 A labeled generalized Büchi automaton is a six-tuple

$$\mathcal{A} = \langle S, S_0, T, A, \Lambda, \mathcal{F} \rangle$$

,

where S is the finite set of states,  $S_0 \subseteq S$  is the set of initial states,  $T \subseteq S \times S$  is the transition relation, A is a finite alphabet for which a set P of atomic propositions is given and  $A = 2^P$ ,  $\Lambda : S \to A$  is the labeling function, and  $\mathcal{F} \subseteq 2^S$  is the set of acceptance conditions.

A run of  $\mathcal{A}$  is an infinite sequence  $\rho = s_0, s_1, \ldots$  over S, such that  $s_0 \in S_0$  and for all  $i \geq 0$ ,  $(s_i, s_{i+1}) \in T$ . A run  $\rho$  is accepting or fair if for each fair set  $F_i \in \mathcal{F}$ , there exists  $s_j \in F_i$  that appears infinitely often in  $\rho$ . The automaton accepts an infinite word  $\sigma = \sigma_0, \sigma_1, \ldots$  in  $A^{\omega}$  if there exists an accepting run  $\rho$  such that for all  $i \geq 0$ ,  $\sigma_i \in \Lambda(\rho_i)$ . The language of  $\mathcal{A}$ , denoted by  $\mathcal{L}(\mathcal{A})$ , is the subset of  $A^{\omega}$  accepted by  $\mathcal{A}$ . Note that the language of  $\mathcal{A}$  is nonempty if and only if  $\mathcal{A}$  contains a reachable fair cycle—a cycle that is reachable from an initial state and intersects with all the fair sets.

We have defined the automata with labels on the states, not on the edges. The automata are called generalized Büchi automata because multiple acceptance conditions are possible. A state s is complete if for every  $a \in A$ , there is a successor s' of s such that  $a \in \Lambda(s')$ . A set of states, or an automaton, is complete if all of its states are. In a complete automaton, any finite state path can be extended into an infinite run. In the sequel all automata are assumed to be complete.

We define the concrete system  $\mathcal{A}$  as the synchronous (or parallel) composition of a set of submodules. Composing a subset of these submodules gives us an over-approximated abstract model  $\mathcal{A}'$ . In symbolic algorithms,  $\mathcal{A}$  and  $\mathcal{A}'$ , as well as the submodules, are all defined over the same state space and agree on the state labels. Communication among submodules then proceeds through the common state space, and composition is characterized by the intersection of the transition relations.

DEFINITION 2.7 The composition  $A_1 \parallel A_2$  of two Büchi automata  $A_1$  and  $A_2$ , where

$$\mathcal{A}_1 = \langle S, S_{01}, T_1, A, \Lambda, \mathcal{F}_1 \rangle ,$$

$$\mathcal{A}_2 = \langle S, S_{02}, T_2, A, \Lambda, \mathcal{F}_2 \rangle ,$$

is a Büchi automaton  $\mathcal{A} = \langle S, S_0, T, A, \Lambda, \mathcal{F} \rangle$  such that,  $S_0 = S_{01} \cap S_{02}$ ,  $T = T_1 \cap T_2$ , and  $\mathcal{F} = \mathcal{F}_1 \cup \mathcal{F}_2$ .

In Figure 2.5, we give an example to show how the automata-theoretic approach for LTL model checking works. The model or Kripke structure in this example corresponds to the circuit in Figure 2.2. We are interested in checking the LTL property  $\phi = \mathsf{F}\,\mathsf{G}\,p$ ; that is, eventually we will reach a point from which the propositional formula p holds for ever.

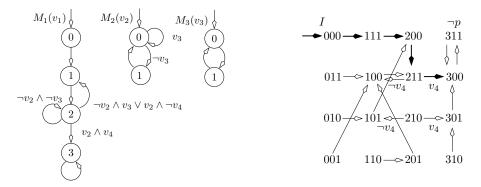

Figure 2.5. An LTL model checking example.

First, we create the property automaton  $\mathcal{A}_{\neg\phi}$  that admits all runs satisfying the negation of  $\phi$ , which is  $\neg\phi$  or  $\mathsf{GF}\neg p$ . Runs satisfying  $\mathsf{GF}\neg p$  must visit states labeled  $\neg p$  infinitely often. There are existing algorithms to translate a general LTL formula to a Büchi automaton; readers who are interested in this subject are referred to [VW86, GPVW95, SB00]. Since our example is simple enough, we do not need to go through the detailed translation algorithm to convince ourselves that the automaton in Figure 2.5 indeed corresponds to  $\mathsf{GF}\neg p$ . In Figure 2.5, states satisfying the acceptance condition are represented as double circles. The property automaton has only one acceptance condi-

tion  $\{0\}$ , meaning that any accepting run has to go through the state 0 infinitely often. We assume that all states in the Kripke structure K are accepting; that is, the acceptance condition of K is  $\{a, b, c, d\}$ .

After composing the property automaton with the model, we have the composed system at the bottom of Figure 2.5, whose acceptance condition is  $\{a0, b0, c0\}$ . Note that in the creation of  $K||\mathcal{A}_{\neg\phi}$  we have used the parallel composition; that is, only transitions that are allowed by both parents are retained. The final acceptance condition is also the union of those of both parents. Since the one for K consists of the entire state space, it is omitted. Finally, we check language emptiness in the composed system by searching for a run that goes through some states in the fair set  $\{a0, b0, c0\}$  infinitely often. It is clear that the language of that system is empty, because no run visits any of these states infinitely often. Therefore, the property  $\phi$  holds in K.

Whether the language of a Büchi automaton is empty can be decided by evaluating the temporal logic property  $\mathsf{EG}_\mathsf{fair}$  true on the automaton. In other words, the language of the composed system is empty if and only if no initial state of the composed system satisfies  $\mathsf{EG}_\mathsf{fair}$  true. The property is an existential CTL formula augmented with a set of Büchi fairness constraints; for our running example,  $\mathsf{fair} = \{\{a0, b0, c0\}\}$ . In a run satisfying this property, a state in every  $F_i \in \mathcal{F}$  must be visited infinitely often. The CTL formula under fairness constraints can be decided by a set of nested fixpoint computations:

$$\mathsf{EG}_{\mathsf{fair}} \, \mathsf{true} = \nu Z. \, \mathsf{EX} \bigwedge_{F_i \in \mathcal{F}} \mathsf{E} \, Z \, \mathsf{U}(Z \wedge F_i) \ ,$$

where  $\nu$  denotes the outer greatest fixpoint computation, and EU represents the embedded least fixpoint computations. When a monotonically increasing transform function f is applied repeatedly to a set Z, we define  $f^{(i)}(Z) = f(f(...f(Z)))$  and declare Z as a least fixpoint if  $f^{(i)}(Z) = f^{(i+1)}(Z)$ . Conversely, when a monotonically decreasing transform function g is applied repeatedly to a set Z, we define  $g^{(i)}(Z) = g(g(...g(Z)))$  and declare Z as a greatest fixpoint if  $g^{(i)}(Z) = g^{(i+1)}(Z)$ . When we evaluate the above formula through fixpoint computation, the initial value of the auxiliary iteration variable Z can be set to the entire universe.

For our running example,

```

\begin{split} F_0 &= \{a0, b0, c0\} \\ Z^0 &= \{a0, b0, c0, a1, b1, c1, a2, b2, c2, a3, b3, c3\} \\ Z^1 &= \mathsf{EX}\,\mathsf{E}\,Z^0\,\mathsf{U}(Z^0\wedge F_0) \\ &= \mathsf{EX}\,\mathsf{E}\{a0, b0, c0, a1, b1, c1, a2, b2, c2, a3, b3, c3\}\,\mathsf{U}\{a0, b0, c0\} \\ &= \mathsf{EX}\{a1, b0\} \\ &= \{a1\} \end{split}

Z^2 &= \mathsf{EX}\,\mathsf{E}\,Z^1\,\mathsf{U}(Z^1\wedge F_0) \\ &= \mathsf{EX}\,\mathsf{E}\{a1\}\,\mathsf{U}\{\ \} \\ &= \mathsf{EX}\{\ \} \\ &= \{\ \} \end{split}

```

Since no state in the composed system satisfies  $\mathsf{EG}_\mathsf{fair}$  true, the language is empty. This method for deciding  $\mathsf{EG}_\mathsf{fair}$  true is known as the Emerson and Lei algorithm [EL86], which is the representative of a class of SCC hull algorithms [SRB02]. In general, the evaluation of EX and EU operators does not have to take the above alternating order; they can be computed in arbitrary orders without affecting the convergence of the fix-point [FFK+01, SRB02]. All SCC hull algorithms share the same worst-case complexity bound — they require  $O(\eta^2)$  symbolic steps, where  $\eta$  is the number of states of the composed model. A symbolic step is either a pre-image computation (finding predecessors through the evaluation of EX) or an image computation (finding successors through the evaluation of EY, the dual of EX).

Another way of checking language emptiness is to find all the strongly connected components (SCCs) and then check whether any of them satisfies all the acceptance conditions. If there exists a reachable non-trivial SCC that intersects every  $F_i \in \mathcal{F}$ , the language of the Büchi automaton is not empty. An SCC consisting of just one state without a self-loop is called *trivial*. In our running example, the reachable non-trivial SCCs of the composed system are  $\{a1\}$  and  $\{c1\}$ . Since none of the non-trivial SCCs intersects the fair set  $\{a0, b0, c0\}$ , the language of the system is empty.

An SCC is a maximal set of states such that there is a path between any two states. A reachable non-trivial SCC that intersects all acceptance conditions is called a fair SCC. An SCC that contains some initial states is called an initial SCC. An SCC-closed set of  $\mathcal{A}$  is the union of a collection of SCCs. The complete set of SCCs of  $\mathcal{A}$ , denoted by  $\Pi(\mathcal{A})$ , forms a partition of the states of  $\mathcal{A}$ . Likewise, the set of disjoint SCC-closed sets can also form a partition of the state space S. A SCC partition  $\Pi_1$  of S is a refinement of another partition  $\Pi_2$  of S if for every SCC or SCC closed set  $C_1 \in \Pi_1$ , there exists  $C_2 \in \Pi_2$  such that  $C_1 \subseteq C_2$ .

An SCC (quotient) graph is constructed from a graph by contracting each SCC into a node, merging parallel edges, and removing self-loops. The SCC graph of  $\mathcal{A}$ , denoted by  $\mathcal{Q}(\mathcal{A})$ , is a directed acyclic graph (DAG); it induces a partial order: the minimal (maximal) SCC has no incoming (outgoing) edge. Reachable fair SCCs, by definition, contain accepting runs that make the language non-empty. Therefore, a straightforward way of checking language emptiness is to compute all the reachable SCCs, and then check whether any of them is a fair SCC.

Observation 2.8 The language of a Büchi automaton is empty if and only if it does not have any reachable fair SCC.

Tarjan's explicit SCC algorithm using depth-first search [Tar72] can be used to decide language emptiness. The algorithm can be classified as an explicit-state algorithm because it traverses one state at a time. Tarjan's algorithm has the best asymptotic complexity bound—linear in the number of states of the graph. However, for model checking industrialscale systems, even the performance of such a linear time algorithm is not be good enough due the extremely large state space. A remedy to the search state explosion is a technique called "on-the-fly" model checking [GPVW95, Hol97], which avoids the construction of the entire state transition graph by visiting part of the state space at a time and constructing part of the graph as needed. Its fair cycle detection is based on two nested depth-first search procedures. Early termination, efficient hashing techniques, and partial order reduction can be used to reduce memory usage during the search and the number of interleavings that need to be inspected. The scalability issue in explict-state enumeration makes them unsuitable for hardware designs, although they have been successful in verifying controllers and software.

Symbolic state space traversal techniques are another effective way of dealing with the extremely large state transition graphs. Instead of manipulating each individual state separately, symbolic algorithms manipulate sets of states. This is accomplished by representing the transition relation of the graph and sets of states as Boolean formulae, and conducting the search by directly manipulating the symbolic representations. By visiting a set of states at a time (as opposed to a single state), symbolic algorithms can traverse a very large state space using a reasonably small amount of time and memory. Thousands or even millions of states, for instance, can be visited in one symbolic step.